Espressif’s ESP32-P4 revision 3.0 and higher has changed pin 54 from NC (non-connected) to a power rail (VDD_HP_1), necessitating several additional passive components and updated firmware.

Espressif Systems first introduced the 400 MHz ESP32-P4 dual-core RISC-V SoC in January 2023, and the official ESP32-P4-Function-EV development board was launched in August 2024. Commercial application rollouts began last year. It would be assumed that both the silicon and associated hardware would no longer change, but this has proven otherwise.

Pin 54’s conversion from NC to VDD_HP_1 seems aimed at enhancing the stability of the high-performance digital domain. The older revisions (1.0, 1.1, and 1.3) are not suggested for new projects, and Espressif recommends using revision 3.0 or 3.1. They issued updated reference schematics with significant adjustments:

The primary disparities between chip revisions v1.0/v1.3 (not recommended for new designs) and v3.0 and newer consist of pin 54’s definition, a 1 MΩ resistor on the DP pin, the addition of two 499 kΩ resistors, and one 22 pF capacitor in the DCDC circuit.

The other diagrams concerning resistors and capacitors do not necessitate a new PCB layout since only component addition or removal is involved. However, the new VDD_HP_1 pin and its surrounding elements might demand a new PCB layout or a makeshift rework using wires and components.

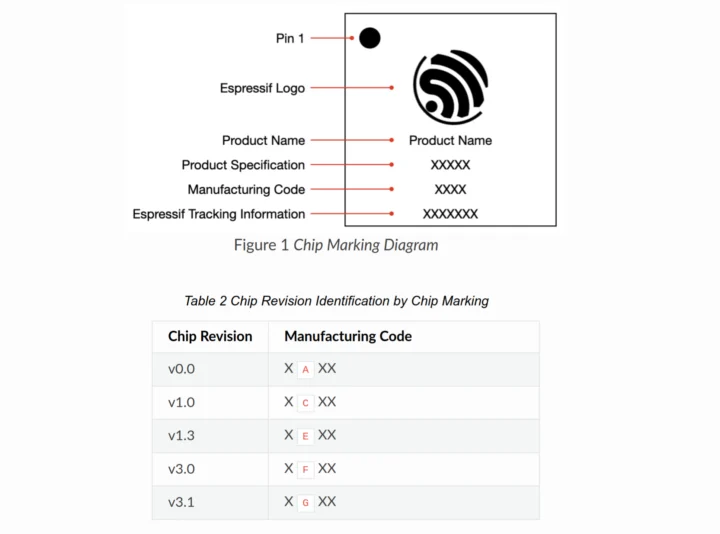

Because Rev 3.x represents a major revision over Rev 1.x, firmware recompilation is required, with CONFIG_ESP32P4_REV_MIN configured appropriately in the ESP-IDF framework. Vendors often label the ESP32-P4 simply as “ESP32-P4,” making it unclear which revision is being provided. Revision details are embedded in the manufacturing code, with Revision 3.0 as XFXX and Revision 3.1 as XGXX.